# DCDC-basierendes Battery-Management-System für LiFePo4-Akkus

#### Idee:

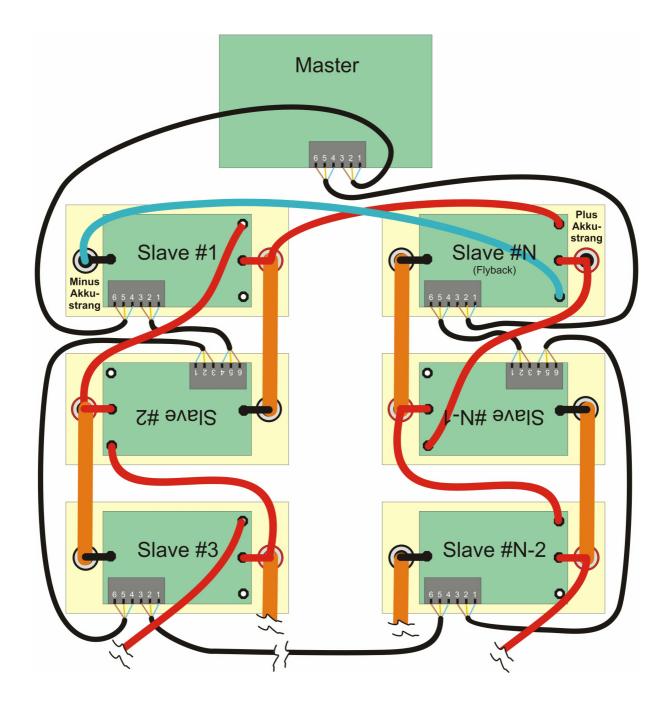

ein selbst entwickeltes Rahmenparameter für (Batterie-Management-System) waren der relativ hohe Preis existierender Systeme und die unschöne Wärmeentwicklung "verbraten" der überschüssigen Ladeleistung an Leistungswiderständen und die damit verbundene starke Wärmeentwicklung mit nicht zu unterschätzender Brandgefahr. Eine mögliche Lösung erschien ein System zu sein, dass eine zu voll werdende Zelle dadurch schützt, dass es aus dieser Zelle Leistung entnimmt und diese der jeweils nächsthöheren Zelle zuführt. Dazu ist in einem Akkustrang für jeden Akku ein einzelner DCDC-Wandler erforderlich. Bis auf den letzten Akku (der am positiven Ende des Strangs sitzt) können dies so genannte "Boost-Wandler" sein. Der letzte Akku erfordert einen "Flyback-Wandler", der aufgrund seiner galvanischen Trennung in der Lage ist die Leistung wieder in den ersten Akku (der am negativen Ende des Strangs sitzt) zurückzuführen.

Die Ladung wird also so lange "im Kreis verschoben", bis sie im Idealfall einen noch nicht vollen Akku trifft, der dadurch dann schneller voll geladen werden kann.

Nach ersten Versuchen mit einer PWM-Chip-Lösung für DCDC-Wandler, dessen Parametrierung und der Eruierung von dessen Problemen und Möglichkeiten wurde beschlossen, den DCDC doch mit Hilfe eines ATMEL-Prozessors und einem festen Pulsverhältnis von 50/50 anzusteuern.

Vorteile der Prozessorlösung bestehen in der Möglichkeit der softwareseitigen Optimierung des Systems, der relativ frei gestaltbaren Überwachungsmöglichkeiten sowie einer Kommunikation der Module untereinander und zu einem Hauptcomputer bzw. zum Ladegerät.

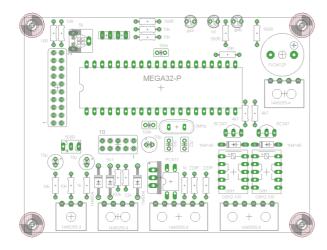

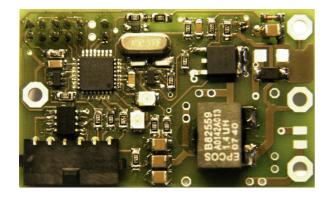

In der finalen Variante wurde ein "Slave"-Board, das auf Basis eines ATmega48 aufgebaut wurde entwickelt. Weiterhin ein "Master"-Board, welches einen ATmega324 (Dual USART) als Basis hat und ein 128x64-Pixel LCD ansteuert.

## Features:

Folgende Features sind in das BMS implementiert (Stand Oktober 2011):

- Slave-Module mit präziser Referenzspannungsquelle.

- 10-Bit Spannungserfassung 0-10,23V mit digitaler Glättung und 10mV Genauigkeit.

- DCDC-Wandler, die bei Überspannung einer Zelle Leistung von der Zelle in die nächsthöhere transportieren.

- Überwachung verschiedener Fehlerzustände (siehe Fehlersicherheit).

- Kommunikation aller Slave-Module und des Mastermoduls untereinander über einen einfachen seriellen 2-Draht-Bus.

- LED-Darstellung der Kommunikation bzw. der Aktivierung des DCDC-Wandlers

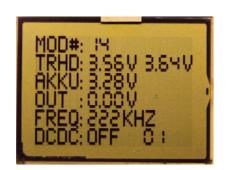

- Möglichkeit zum Anschluss einen Debugging-Status-Displays an jedes Slave-Modul mit Anzeige von:

- Modulnummer

- Zellspannung

- Upper- und Lower Threshold

- DCDC-Frequenz

- Ausgangsspannungsüberwachung

- Modul-Status

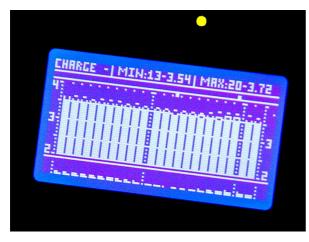

- Überwachung und Darstellung der Zellspannung eines jeden Akkus.

- Darstellung von minimaler und maximaler aufgetretener Spannung der einzelnen Zellen.

- Numerische und grafische Darstellung der jeweils höchsten und niedrigsten Zelle.

- Darstellung, welches Modul auf "Balancing" steht.

- Erfassung ein Darstellung der Balancingzeiten der einzelnen Module.

- Frei einstellbare Warn- und Abschaltschwellen für Unterbzw. Überspannung der Zellen.

- Grafische Darstellung des Betriebszustands:

- Drive

- Charge (Full)

- Charge (Balance)

- Charge (Off)

- Error.

- Anzeige welches Modul einen DCDC-Ausgangsspannungs-Leerlauf verursacht hat.

- "One-Touch" Updatemöglichkeit aller Slave-Thresholds

- Vorbereitung für Bluetooth-Kommunikation zu externen Devices.

## Kommunikation zwischen den Modulen:

Die Kommunikation zwischen den einzelnen Modulen erfolgt über einen galvanisch getrennten seriellen Bus. Um den Verkabelungsaufwand zu minimieren, und um über lange Strecken steile Signalflanken aufrecht zu erhalten, arbeitet jedes Modul als aktiver Signalrepeater. Das bedeutet, dass jedes Modul Daten über den seriellen Eingang empfängt, ggf. softwareseitig auswertet und anschließend wieder über den seriellen Ausgang verschickt.

Die galvanische Trennung erfolgt über einen Optokoppler jeweils am Eingang eines Moduls und einem Vorwiderstand jeweils am Ausgang eines Moduls, welcher so dimensioniert ist, dass exakte Signalflanken bis zu einer Betriebsspannung von 2,5V herunter möglich sind.

#### Power-On-Logik:

Alle Bestandteile des Systems sind so ausgelegt, dass im Ruhezustand kein (!) Strom verbraucht wird. Dadurch kann das System beliebig lange an den Akkus montiert bzw. im Fahrzeug verbleiben, ohne dass eine Tiefentladung der Akkus zu befürchten ist.

Ohne Aktivierung des Systems ist somit jedoch auch keine Akkuüberwachung / -schutzfunktion möglich, so dass das Ladegerät vom Mastermodul aktiv eingeschaltet werden muss.

Die Power-On Logik, erfolgt durch eine Steuerspannung, die zunächst vom Master über einen Port vom Master ausgegeben wird und im ersten Slave einen Optokoppler durchschalten lässt, der wiederum das erste Slavemodul aktiviert. Das Einschalten des ersten Slaves durch einen Port ermöglicht das softwareseitige "resetten" alles Slaves, falls dies irgendwann als nötig erscheinen sollte.

Jedes aktivierte Slavemodul gibt durch seine eigene Betriebsspannung ebenfalls ein Steuersignal an das jeweils folgende Slavemodul und aktiviert dieses.

Die Steuerspannung des letzten Slavemoduls läuft in's Leere.

#### Fehlersicherheit / Redundanz:

Folgende Überlegungen zur Fehlersicherheit bzw. Redundanz wurden getroffen:

- Slaves gehen auf "Sleep", wenn über 5 Sekunden keine Kommunikation vom Master erfolgt (siehe auch unten -Probleme)

- Leiterbahnsicherungen primär und sekundärseitig brennen durch, wenn z.B. die Gleichrichterdiode oder der DCDC-FET durchlegieren.

- Die Ausgangsspannung der Boost-Wandler werden grob überwacht und das Modul geht auf "Error", wenn sie zu hoch wird. Dadurch wird ein Heißwerden des leer laufenden DCDC vermieden und der Master über den Fehler benachrichtigt, der die Ladung abbrechen kann.

- Wenn die Module nicht kommunizieren geht der Master auf Timeout und deaktiviert die Ladung.

- Reset aller Module durch den Master ist möglich (über Power on/off).

- Softwareseitige obere und untere Grenzen der DCDC-Schaltfrequenzen verhindern unkontrollierte Funktion durch falsches Auslesen des EEPROMs.

- Frei einstellbare Umschalt- und Abschaltzeiten für Hauptladung / Balancingladung.

## Folgende Probleme sind existent und nur teilweise gelöst:

Sollte ein Slave ohne Steuerspannung aktiv werden (Einschalt-FET durchlegiert), so aktiviert dieses Modul auch alle Module dahinter, da die Modulaktivierung rein hardwaremäßig erfolgt.

Teilweise Lösung: Die Slaves haben ein Timeout und gehen auf "Sleep", wenn 5 Sekunden lang keine Kommunikation erfolgt. Dadurch wird der Stromverbrauch des Moduls auf 9mA reduziert und eine Kommunikation bis zum Hard-Reset unterbunden. Eine gelbe LED zeigt den Fehler dauerhaft an (2mA). Die hart verdrahtete Steuerspannung zum Einschalten des folgenden Moduls benötigt 7mA. Durch die unterbundene Kommunikation wird der Fehler beim nächsten Einschalten des Masters detektiert, da die Slaves nicht mehr kommunizieren. Der Stromverbrauch von 9mA entlädt einen 100Ah-Akku erst in etwas über einem Jahr. Bis dahin sollte der Fehler bemerkt werden.

Endgültiger Lösungsvorschlag: Das jeweils folgende Modul könnte softwareseitig über einen Ausgangsport des Moduls

aktiviert werden. Dadurch kann der Sleep-Zustand des Prozessors den Stromverbrauch eines Slaves in den Bereich auf ca. 1mA reduzieren (mit Warn-LED an, +2mA) und somit die Akku-Entladung auf 3-5 Jahre verlängern. Auch ohne Warn-LED kann das defekte Modul schnell gefunden werden, da die Kommunikation bei diesem "stecken bleibt" und ab dem betroffenen Modul bei der Kommunikation keine Status LEDs mehr blinken

#### Funktionsbeschreibung Gesamtsystem:

#### Hardware:

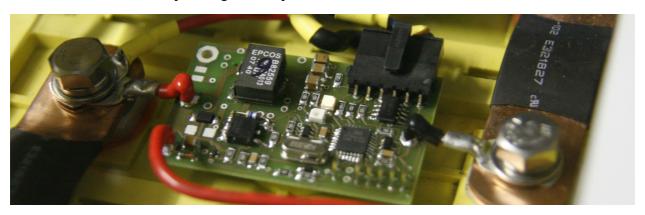

Jedes Modul verfügt über einen DCDC-Wandler, der den jeweils folgenden Akku speist. Das letzte Modul im Strang speist den ersten Akku im Strang (siehe Signalfluss).

Der verwendete Boost-Wandler hat einen Wirkungsgrad von ca. 75% und ist von der Schaltfrequenz so eingestellt, dass er ca. 10W Primärleistung benötigt.

Dadurch passiert folgendes:

- Der zu balancende Akku (z.B. Akku5) wird zunächst mit 10W/3,65V=2,7A (=Primärstrom des DCDC) belastet.

- Der nächsthöheren Akku (Akku6) und der zu balancende (Akku5) werden mit ca. 7,5W also 7,5W/7,3V=1A (=Sekundärstrom des DCDC) geladen.

- Die 1A Ladestrom subtrahieren sich im zu balancenden Akku (Akku5) von den 2,7A Entladestrom, so dass der zu balancende Akku nur mit 1,7A belastet wird.

- Geht der jeweils darunterliegende Balancer (Akku4) auch an, so lädt dieser den Akku5 mit ebenfalls 1A, so dass der Balancer (im Akku 5) "nur" noch 0,7A abführt.

- Im Falle des Flyback-Wandlers (letztes Modul) ist der Wirkungsgrad etwa 65% und das Übersetzungsverhältnis 1:1. Dadurch ergibt sich bei einem Sekundärstrom von 1A ein Primärstrom von ca. 1,55A was von den Werten wiederum ähnlich den Boost-Modulen ist.

#### Software:

Durch Senden des 9-Bit-Adress-Datenworts "1" wird das erste Modul vom Master aufgefordert seine Spannung und seinen Status zu senden. Dies passiert in Form von zwei 8-Bit-Datenworten. An die zwei Datenworte hängt das angesprochene Modul ein 9-Bit-Adress-Datenwort mit Modulnummer+1 und spricht somit das zweite Modul an.

Jedes Modul reagiert nur auf Adress-Datenworte, dessen Nummer mit der moduleigenen Nummer übereinstimmt.

**Alle** empfangenen Datenworte werden immer unverändert wieder auf den seriellen Ausgang geschrieben, so dass jedes Modul automatisch auch als Repeater dient.

Am Ende der Kette kommt folgendes Protokoll am Master an:

Der Master muss nun softwareseitig sicherstellen, dass aufgrund des Protokolls die richtigen Werte den richtigen Modulen zugeordnet werden und dass die letzte Modulnummer ignoriert wird. Die passiert im einfachsten Fall so, dass bei einer empfangenen Modulnummer (9-Bit) ein Adresspointer gesetzt wird und die zwei folgenden Daten-Werte dorthin geschrieben werden. Folgt einer Modulnummer eine weitere Modulnummer, wird einfach nur der Adresspointer neu gesetzt.

Die Modulnummer 255 ist reserviert für ein Reprogramming des Slave-Thresholds.

### Master-Modul:

### Schaltung:

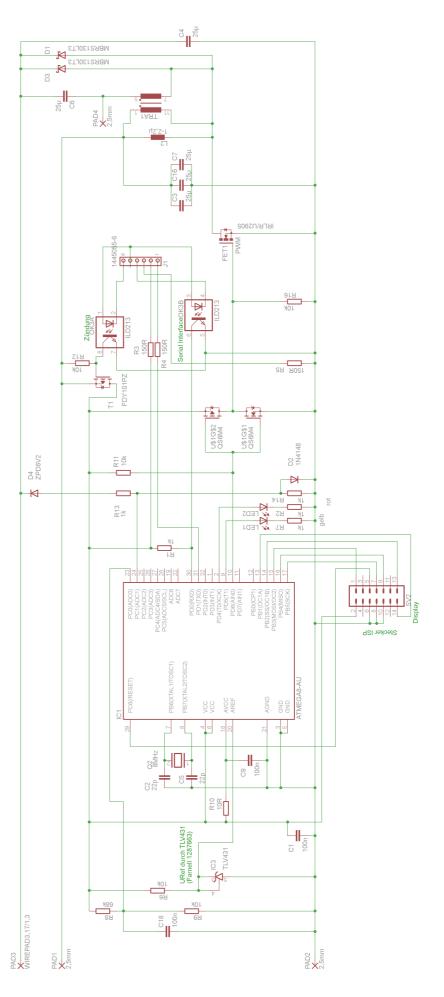

Das Schaltbild ist in Anhang 1 zu sehen.

### Funktionsbeschreibung Master:

Der Master verfügt über eine duale Spannungsversorgung (J3), welche über Dioden oder-verknüpft das System mit Spannung versorgt. Der Eingangsspannungsbereich liegt zwischen 8 und 30V, da ein DCDC-Wandler (IC1) diese Spannung auf 5V für den Prozessor runter regelt. **ACHTUNG**: Bitte darauf achten, dass Ladegerät und Zündung eine gemeinsame Masse haben

oder dass eine entsprechende galvanische Trennung von Zündungsplus und Ladegerätversorgung gegeben ist!

Jenachdem welche Eingangsspannung das System gestartet hat, kann zwischen "Drive" (Zündungsplus) und "Charge" (Ladegerätspannung) unterschieden werden. Den Status übermittelt der Spannungsteiler R8 und R9 zusammen mit der Überspannungsschutzdiode D3(5,1V).

Über den Port PA3 wird ein Lo-Signal ausgegeben, um den ersten Slave zu aktivieren. LED3 zeigt den Stromfluss zum ersten Modul an.

Anschließend wird das erste Modul adressiert und der Datenstrom abgewartet, der die Zelldaten liefert.

Die Darstellung aller relevanten Daten erfolgt über das 128x64-Punkte Display.

Zwei 1xUm-Relais (K1 und K2) können in der Software frei zugewiesen werden und z.B. das Ladegerät anschalten bzw. runter schalten (J5).

LED 1 stellt zusammen mit einem Buzzer das Alarmsignal optisch und akustisch zur Verfügung. LED2 dient als Status-LED (z.B. "Balancing on")

Es ist ein Eingang (J2) für einen Strom-Sensor vorgesehen (R10, R11, R12, R13, C3 und C4), so dass der Master auch zur Kapazitäts- / Verbrauchsanzeige erweitert werden kann. Weiterhin ist ein zweiter Logic-Level-UART vorhanden, der über J6 zum Ansteuern eines zusätzlichen seriellen Moduls (z.B. Bluetooth) dient. **ACHTUNG:** Hier ist ein Schaltplan-Fehler bitte mit Datenblatt des **ATmega324P** abgleichen!

Jumper JP1 und JP2 dienen zum Anschluss von zwei Tastern, die in der Software frei zugewiesen werden können.

Als Display wurde ein Modul mit S6B0107 / S6B0108-Treibern eingesetzt. Für die Hinterleuchtung dienen R14 und R15 als Vorwiderstände. R6 stellt den Displaykontrast ein.

Am Stecker J1 gilt:

- 1: Serial Out

- 2: +Akku

- 3: PA3-Out / Active-Low (für Power-On nächstes Modul)

- 4: Serial in

- 5: gemeinsames Plus für Serial-In und Power-On-In

- 6: N.C

Alle Module (auch der Master) werden immer folgendermaßen verkabelt:

- 1 -> 4

- 2 -> 5

- 3 -> 6

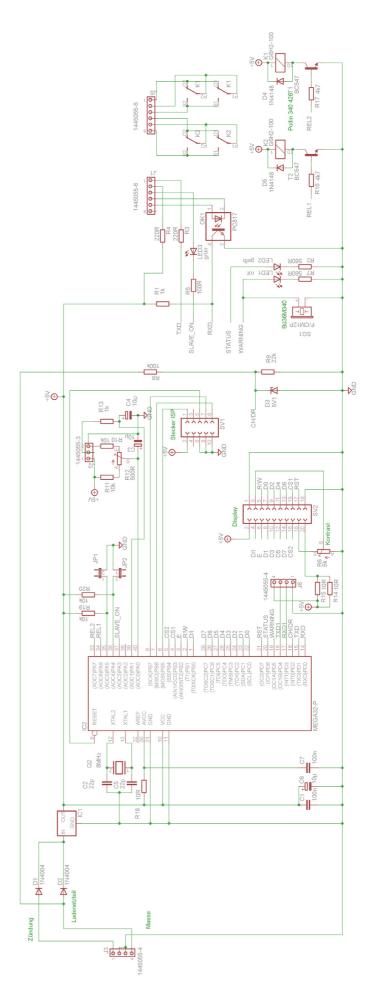

#### Slave-Module:

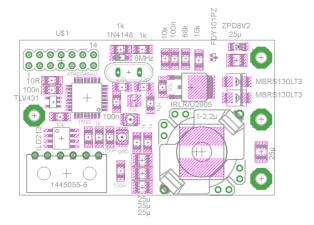

#### Schaltung:

Das Schaltbild ist in Anhang 2 zu finden

#### Funktionsbeschreibung Slave:

Zentrales Element der Slaves ist der ATmega48, der mit 8MHz aus einem Quarz versorgt wird. Der Quarz ist erforderlich, da der interne Takt des ATmega stark mit der Betriebsspannung (vom Akku. 2,5-4,0V) schwankt und dadurch die serielle Kommunikation nicht mehr gewährleistet wäre.

Der Prozessor bekommt eine externe Spannungsreferenz durch den LTV431, welche bei 1,24V liegt. Auch dies ist dem stark schwankenden Betriebsspannungsbereich des Prozessors zu schulden.

Die Einschaltlogik besteht aus dem Optokoppler OK3A (1/2 ILD213), dem FET T1 (FDY101PZ) und dem Pullup-Widerstand R12

Die Akkuspannung wird über den Spannungsteiler R8 und R9 herunter geteilt (÷ 7,8) und dem A/D-Eingang ADC0 zugeführt, so dass 0-9,672V insgesamt gemessen werden können. Nach einer internen Umrechnung mit dem Faktor ·0,9454555 ergibt sich daraus eine Darstellung von 1LSB=10mV. Gemessen wird in der Praxis immer nur ein Akku mit 0-4V.

D4 (8,2V), R13, R14 und D2 sorgen dafür, dass der A/D-Eingang ADC1 eine Spannung erhält, wenn der DCDC-Ausgang über 9V steigt (Leerlaufschutz)

Der Treiber QS6M4 verstärkt den DCDC\_Takt für den Schalt-FET IRLR2905, welcher entweder die Spule L2 (Boost) oder den Trafo TRA1 ansteuert.

ACHTUNG! Im Falle der Trafoansteuerung ist die Brücke zwischen Primär- und Sekundärseite des Trafos auf der Platine aufzutrennen (Ausbohren der Durchkontaktierung zwischen den Anoden von D1 und D3).

Die Diode D1 richtet die Ausgangsspannung des DCDC gleich. Sie kann bei Bedarf durch D3 verstärkt werden, wenn höhere Ströme gewünscht sind.

Der Stecker SV2 dient zum Programmieren des Moduls sowie dem Anschluss eines Nokia 3310-Displays für Statusinformationen

Zusätzlich zu den angegeben Bauteilen wurde noch ein Snubber verbaut, der mit  $4,7\Omega$  und 470pF dimensioniert wurde. Im Flyback-Wandler beträgt die Kapazität 2nF.

Belegung J1 (Im Bild links ist 1 ganz rechts und 6 ganz links):

- 1: Serial Out

- 2: +Akku

- 3: Masse-Out (für Power-On nächstes Modul)

- 4: Serial in

- 5: gemeinsames Plus für Serial-In und Power-On-In

- 6: Power-On-In (Active Low)

Alle Module (auch der Master) werden immer folgendermaßen verkabelt:

- 1 -> 4

- 2 -> 5

- 3 -> 6

# Signalfluss des Gesamtsystems:

# **ANHANG1 - Schaltbild Master**

# **ANHANG2 - Schaltbild Slave**